Instruction-Address-Misaligned Exceptions

Today’s @risc_v Tip:

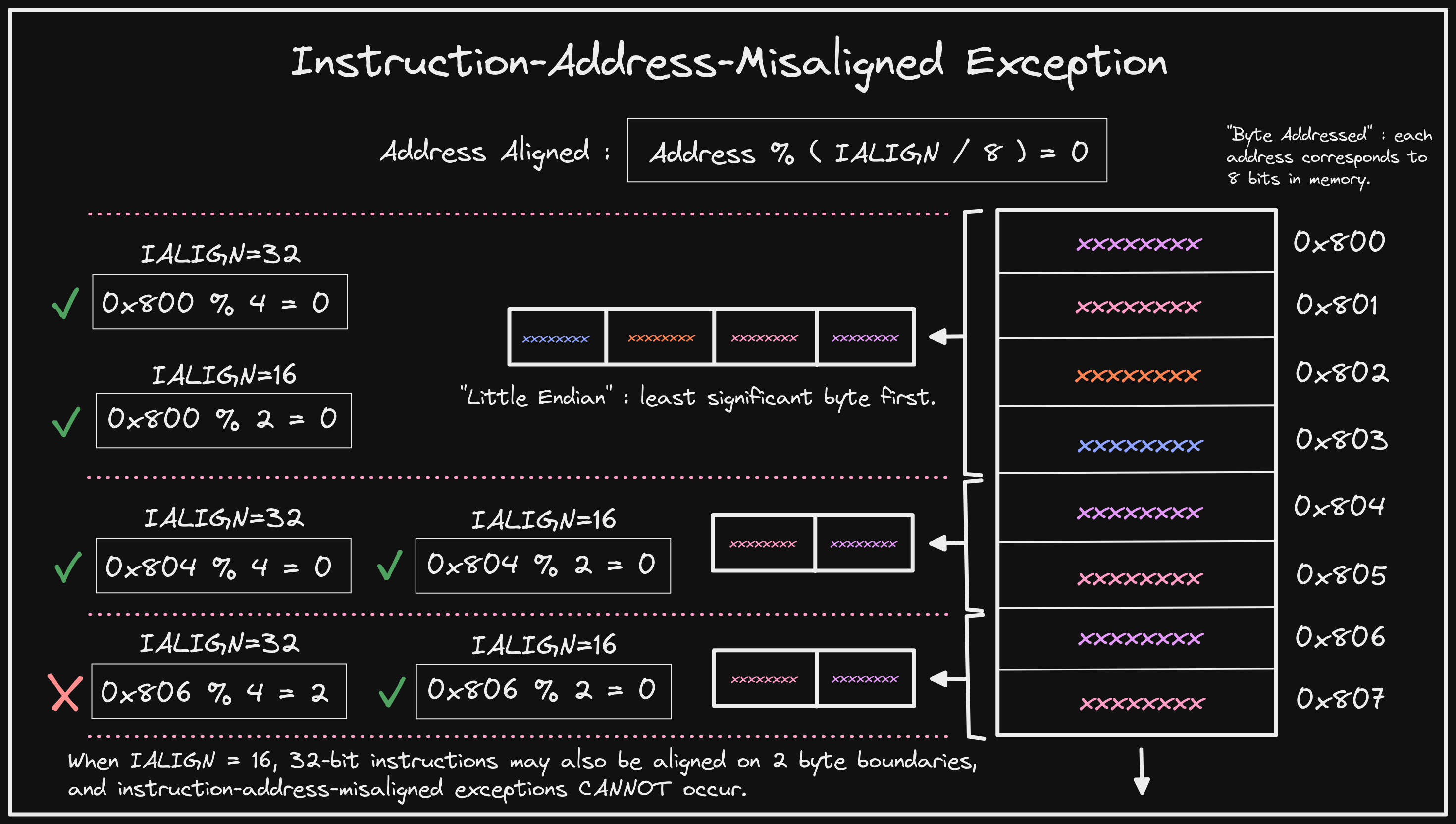

Instruction-Address-Misaligned exceptions can occur when a control transfer instruction (e.g. branch / jump) provides a misaligned target. The base ISA specifies 4 byte alignment (IALIGN=32), but extensions (such as C) may relax to 2 bytes (IALIGN=16).