RISC-V Weak Memory Ordering

Today’s @risc_v Tip:

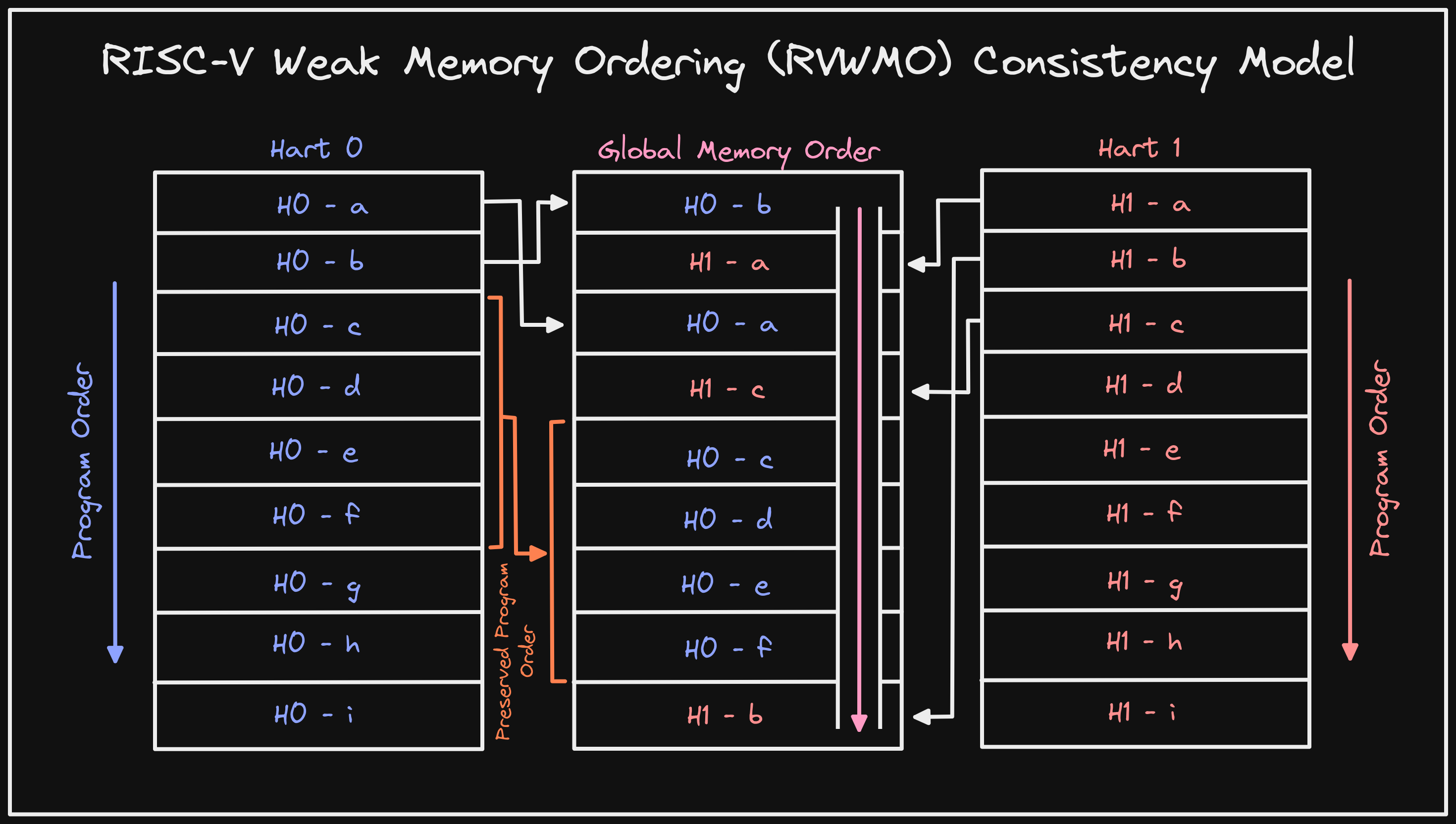

RISC-V defines its memory model (RVWMO) in the context of 3 orderings:

- Program Order: order of ops performed by a single hart

- Global Memory Order: order of ops performed by all harts

- Preserved Program Order: subset of program order respected globally

This diagram is an abstract example, but the key points are illustrated: memory operations appear to perform sequentially in the context of a single hart, but may not be observed in the same order globally. RVWMO defines which operations in a program order are respected globally.

RVWMO is specified by a series of preserved program order rules in the following categories:

- Overlapping-Address Orderings

- Explicit Synchronization

- Syntactic Dependencies

- Pipeline Dependencies

And memory model axioms:

- Load Value Axiom

- Atomicity Axiom

- Progress Axiom